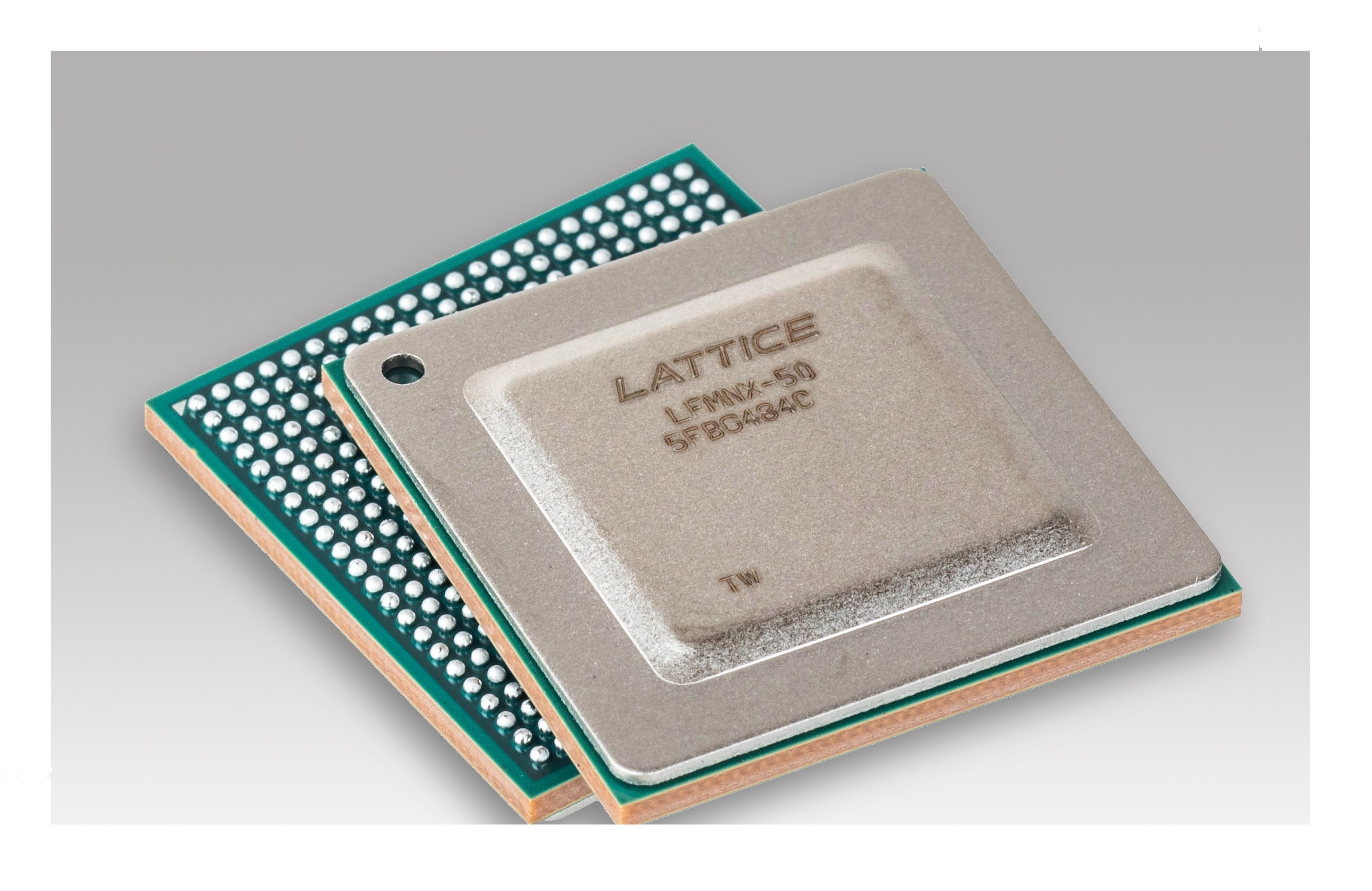

Второе поколение ПЛИС Mach от Lattice Semiconductor имеет повышенные функции безопасности и возможности обработки для реализации операции аппаратного корня доверия (HRoT) в реальном времени для серверов, вычислений, коммуникаций, промышленных и автомобильных систем. ПЛИС Mach-NX основаны на платформе ПЛИС Nexus компании.

Чтобы предотвратить попытки злоумышленников использовать уязвимости прошивки, системы могут быть защищены с помощью HRoT в реальном времени и поддержки более сильных алгоритмов криптографии, таких как ECC 384, а также надежных протоколов безопасности данных для защиты платформ от кибератак и краж IP.

ПЛИС Mach-NX объединяют безопасный анклав (384-битный аппаратный криптографический движок, поддерживающий перепрограммируемую защиту потока битов) с логической ячейкой и блоком ввода-вывода. Защищенный анклав помогает защитить микропрограммное обеспечение, а блок LC и ввода-вывода обеспечивает функции управления системой, такие как управление питанием и управление вентиляторами. ПЛИС могут проверять и устанавливать беспроводные обновления микропрограмм, чтобы гарантировать соответствие систем последним рекомендациям и протоколам безопасности. Архитектура параллельной обработки и флеш-память с двойной загрузкой, как утверждается, обеспечивают практически мгновенное время отклика, необходимое для обнаружения атак и восстановления после них.

ПЛИС поддерживают набор настраиваемого встроенного программного обеспечения Lattice Sentry , эталонные конструкции, IP и инструменты разработки для ускорения внедрения безопасных систем, совместимых с NIST.

ПЛИС имеют до 11k логических ячеек и до 379 операций ввода-вывода и настраиваются с помощью инструмента Lattice Propel . Эта среда разработки на основе графического интерфейса пользователя позволяет разработчикам создавать решения для обеспечения устойчивости микропрограмм платформы (PFR), сводя к минимуму необходимость написания кода RTL.

Еще одна функция безопасности для OEM-производителей — это услуга подписки на безопасность цепочки поставок Lattice SupplyGuard. Это отслеживает заблокированные FPGA на протяжении всего их жизненного цикла, от производства до транспортировки, системной интеграции и сборки, начальной настройки и развертывания.

Личный кабинет

Личный кабинет

Загрузка

Загрузка